演講/活動

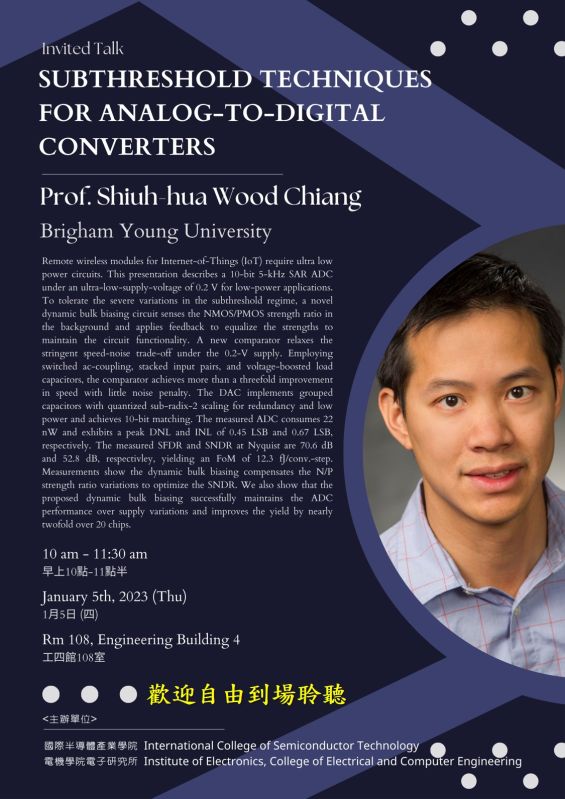

2022-12-29 11:31:41陳秋雲【演講公告】Subthreshold Techniques for Analog-to-Digital Converters~~主講:Professor Shiuh-hua Wood Chiang(江

~~~歡迎自由到場聆聽~~~

時間:2023年1月5日(四) 上午10:00-11:30

地點:陽明交通大學工程四館一樓108室知新廳

<Abstract>

Remote wireless modules for Internet-of-Things (IoT) require ultra low power circuits. This presentation describes a 10-bit 5-kHz SAR ADC under an ultra-low-supply-voltage of 0.2 V for low-power applications. To tolerate the severe variations in the subthreshold regime, a novel dynamic bulk biasing circuit senses the NMOS/PMOS strength ratio in the background and applies feedback to equalize the strengths to maintain the circuit functionality. A new comparator relaxes the stringent speed-noise trade-off under the 0.2-V supply. Employing switched ac-coupling, stacked input pairs, and voltage-boosted load capacitors, the comparator achieves more than a threefold improvement in speed with little noise penalty. The DAC implements grouped capacitors with quantized sub-radix-2 scaling for redundancy and low power and achieves 10-bit matching. The measured ADC consumes 22 nW and exhibits a peak DNL and INL of 0.45 LSB and 0.67 LSB, respectively. The measured SFDR and SNDR at Nyquist are 70.6 dB and 52.8 dB, respectivley, yielding an FoM of 12.3 fJ/conv.-step. Measurements show the dynamic bulk biasing compensates the N/P strength ratio variations to optimize the SNDR. We also show that the proposed dynamic bulk biasing successfully maintains the ADC performance over supply variations and improves the yield by nearly twofold over 20 chips.

<Biography>

Shiuh-hua Wood Chiang received his B.S. degree in Computer Engineering from the University of Waterloo, Waterloo, Canada in 2007, the M.S. degree in Electrical Engineering from the University of California, Irvine in 2009, and the Ph.D. degree in Electrical Engineering from the University of California, Los Angeles in 2013. He was a Postdoctoral Scholar in the Communication Circuits Laboratory at the University of California, Los Angeles in 2013. From 2013 to 2014 he was a Senior Design Engineer in the RFIC design group in Qualcomm, developing low-power circuits for Bluetooth transceivers. He joined the Department of Electrical and Computer Engineering of Brigham Young University in 2014. His research interests include low-power RF/analog/mixed-signal circuits for communications and sensing applications.

主辦單位:陽明交大國際半導體產業學院、電機學院電子研究所